# Vivado从此开始(To Learn Vivado From Here)

#### 本书围绕Vivado四大主题

- 设计流程

- 时序约束

- 时序分析

- Tcl脚本的使用

作者: 高亚军 (Xilinx战略应用高级工程师)

- 2012年2月,出版《基于FPGA的数字信号处理(第1版)》

- 2012年9月,发布网络视频课程《Vivado入门与提高》

- 2015年7月,出版《基于FPGA的数字信号处理(第2版)》

- 2016年7月,发布网络视频课程《跟Xilinx SAE学HLS》

◆ 内容翔实全面: 涵盖Vivado所有基本功能

◆ 讲解深入浅出:结合大量案例,帮助读者加强对基本概念的理解

◆ 描述图文并茂:给出具体操作步骤,易于快速动手实践

#### XILINX > ALL PROGRAMMABLE...

# **ALL PROGRAMMABLE**

### **Vivado Implementation**

Lauren Gao

## Agenda

- > New Feature: Directive

- > Implementation Strategy

- Run Implementation in Project-Mode and Non-Project Mode

## Agenda

#### > New Feature: Directive

- > Implementation Strategy

- Run Implementation in Project-Mode and Non-Project Mode

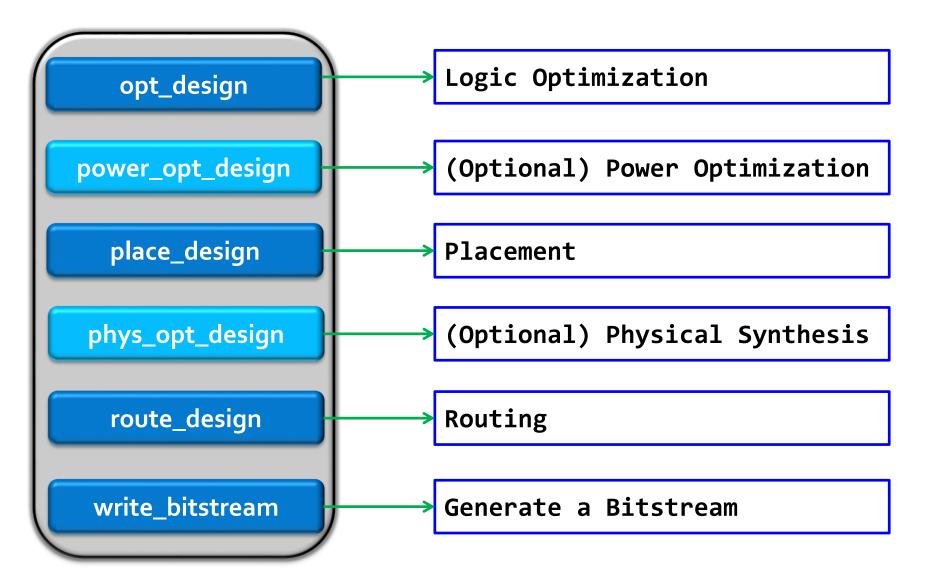

# **Vivado Implementation Sub-processes**

XILINX > ALL PROGRAMMABLE.

# **New Feature: Directive**

| 🗆 Opt Design (o | pt_design)                                  |  |  |

|-----------------|---------------------------------------------|--|--|

| is_enabled      | <b>V</b>                                    |  |  |

| tcl.pre         |                                             |  |  |

| tcl.post        |                                             |  |  |

| -verbose        |                                             |  |  |

| -directive      | Default 🔻                                   |  |  |

| More Options    | Explore                                     |  |  |

| directive       | ExploreArea<br>AddRemap<br>RuntimeOptimized |  |  |

|                 | Default                                     |  |  |

| Place Design            | (place_design)                                                     |

|-------------------------|--------------------------------------------------------------------|

| tcl.pre                 |                                                                    |

| tcl. <mark>p</mark> ost |                                                                    |

| -no_timing_driv         | ven                                                                |

| -no_drc                 |                                                                    |

| -directive              | Default                                                            |

| More Options            | Explore                                                            |

| directive               | WLDrivenBlockPlacement<br>LateBlockPlacement<br>ExtraNetDelay high |

|                         | ExtraNetDelay medium                                               |

|                         | ExtraNetDelay_low                                                  |

|                         | SpreadLogic_high                                                   |

|                         | SpreadLogic_medium                                                 |

#### Command option to "direct" behavior towrd alternate goal

- Different algorithms

- Different objectives

#### > Implementation commands with –directive

opt\_design, place\_design, phys\_opt\_design, route\_design

#### > Alternative flows to use

- When the default flow does not meet design goals

- When tool runtime increase can be accommodated

#### Uses different algorithms

- Not random seeds like ISE cost tables

- More consistent and predictable behavior

- Help -opt\_design to find all the directives

#### XILINX ➤ ALL PROGRAMMABLE.

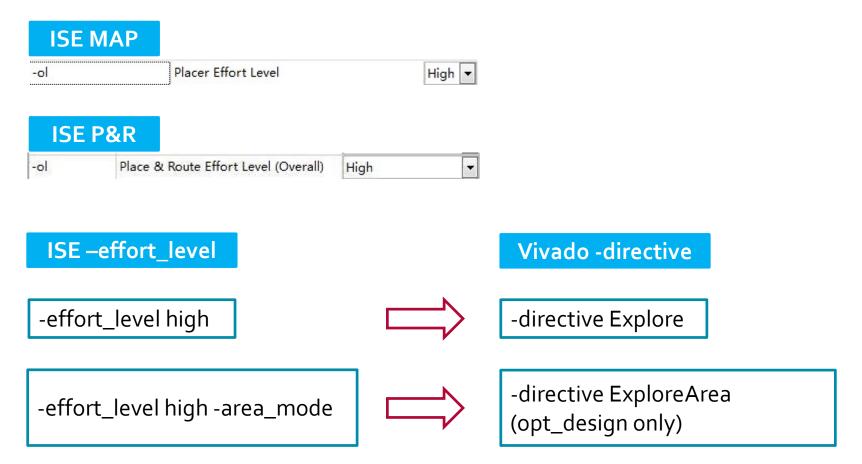

# -directive Explore

#### > All commands have –directive Explore

XILINX > ALL PROGRAMMABLE.

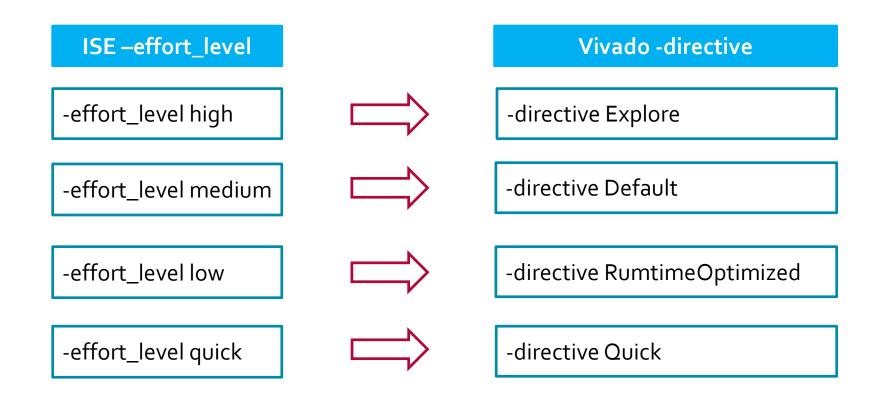

# -directive: Replacement for \_effort\_level

#### > Automatic mapping for all implementation commands

XILINX > ALL PROGRAMMABLE..

# Agenda

- > New Feature: Directive

- > Implementation Strategy

- Run Implementation in Project-Mode and Non-Project Mode

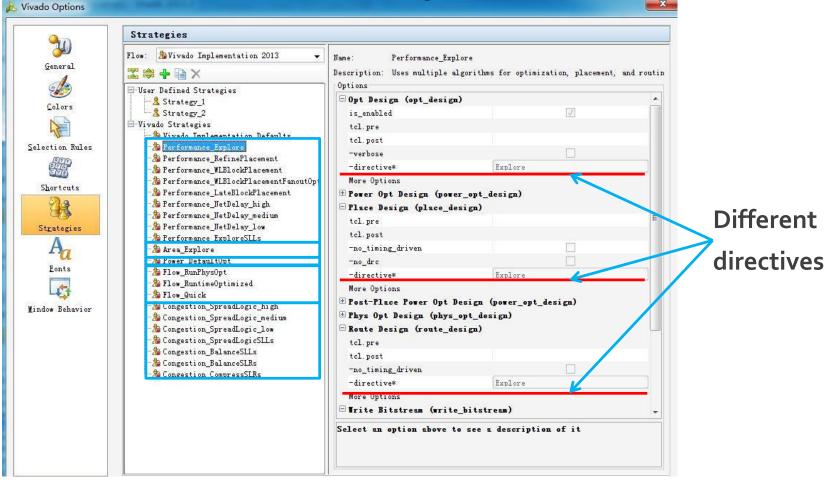

# **Implementation Strategy**

> Tools  $\rightarrow$  options  $\rightarrow$  Strategies

#### > Strategies are grouped by category

- Performance, Area, Power, Flow, Congestion

# **Strategies Example**

| Design flow                      | Performance_Explore | Area_Explore | Power_DefaultOpt | Flow_RunPhysOpt | Congestion_SpreadLogic_high |

|----------------------------------|---------------------|--------------|------------------|-----------------|-----------------------------|

| opt_design                       | $\checkmark$        | $\checkmark$ | $\checkmark$     | $\checkmark$    | $\checkmark$                |

| -directive                       | Explore             | ExploreArea  | Default          | Default         | Default                     |

| power_opt_design                 | ×                   | ×            | $\checkmark$     | ×               | ×                           |

| place_design                     | $\checkmark$        | $\checkmark$ | $\checkmark$     | $\checkmark$    | √                           |

| -directive                       | Explore             | Default      | Default          | Default         | SpreadLogic_high            |

| power_opt_design<br>(post-place) | ×                   | ×            | ×                | ×               | ×                           |

| phys_opt_design                  | $\checkmark$        | ×            | $\checkmark$     | $\checkmark$    | $\checkmark$                |

| -directive                       | Explore             |              | Default          | Explore         | AggressiveFanoutOpt         |

| route_design                     |                     |              |                  |                 |                             |

| -directive                       | Explore             | Default      | Default          | Default         | MoreGloballterations        |

> Directives -> command level behavior

Strategies -> implementation run-level behavior, a combination of directives

# **Implementation Strategy**

- Different strategy may have

- Different directives

- Vivado implementation default: -directive are all default

- Performance\_Explore: -directive are all Explore

- Different design flows

- Vivado implementation default: opt\_design, place\_design , route\_design

- Performance\_Explore: opt\_design, place\_design, phys\_opt\_design, route\_design

- > Each strategy has different directives for the impl command steps

- You can customize your own strategy

- User defined strategies

- The Performance\_Explore strategy is a good first choice, because it covers all types of designs

- The Performance strategies aim to improve design performance at the expense of runtime

- Strategies containing the terms SLL or SLR are for use with SSI devices only

E XILINX > ALL PROGRAMMABLE.

# **Tcl API**

| is_enabled          | <b>V</b>                                                          |  |

|---------------------|-------------------------------------------------------------------|--|

| tcl.pre<br>tcl.post | Tcl API                                                           |  |

| -verbose            |                                                                   |  |

| -directive          | Default                                                           |  |

| More Options        | Explore<br>ExploreArea<br>AddRemap<br>RuntimeOptimized<br>Default |  |

Place Design (place design)

#### All implementation sub-processes have Tcl API

- tcl.pre : commands should be executed before this process

- tcl.post: commands should be executed after this process

#### > Example

opt\_design.tcl

1 set mydir [get\_property DIRECTORY [current\_project]]

2 set prjname [get\_property NAME [current\_project]]

3 report\_utilization -file \$mydir/opt\_design\_util.txt

4 report\_timing\_summary -file \$mydir/opt\_design\_timing.txt

5 write\_checkpoint \$mydir/\${prjname}\_opt\_design -force

| tcl. pre<br>tcl. post<br>-no_timing_dri<br>-no_drc                                                                                                                                | Tcl API                |                  |             | <pre>summary -file \$mydir/opt_design_timing.t<br/>nt \$mydir/\${prjname}_opt_design -force</pre> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------|-------------|---------------------------------------------------------------------------------------------------|

| -directive                                                                                                                                                                        | Default                | +                |             |                                                                                                   |

| More Options Explore<br>WLDrivenBlockPlacement<br>LateBlockPlacement<br>ExtraNetDelay_high<br>ExtraNetDelay_medium<br>ExtraNetDelay_low<br>SpreadLogic_high<br>SpreadLogic_medium | •                      | 🗆 Opt Design (op | t_design)   |                                                                                                   |

|                                                                                                                                                                                   | WLDrivenBlockPlacement | Ε                | is_enabled  |                                                                                                   |

|                                                                                                                                                                                   | LateBlockPlacement     |                  | tcl.pre     |                                                                                                   |

|                                                                                                                                                                                   |                        |                  | tcl.post    | F:\Vivado\Iutorial\logic_sim\ISim_Iutorial\opt_design.tcl 📀                                       |

|                                                                                                                                                                                   |                        |                  | -verbose    |                                                                                                   |

|                                                                                                                                                                                   | xtraNetDelay_low       | -directive*      | ExploreArea |                                                                                                   |

|                                                                                                                                                                                   | SpreadLogic_high       | -                |             | Exprotence                                                                                        |

|                                                                                                                                                                                   | More Options           |                  |             |                                                                                                   |

#### XILINX ➤ ALL PROGRAMMABLE.

# Agenda

- > New Feature: Directive

- Implementation Strategy

- Run Implementation in Project-Mode and Non-Project Mode

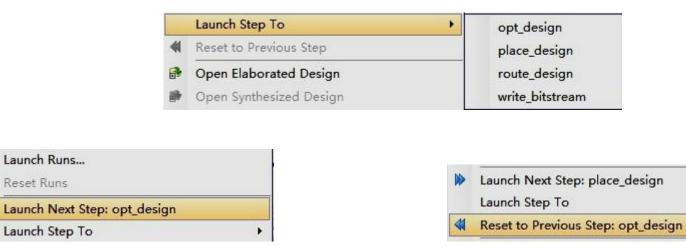

# Run Implementation in Project Mode with GUI

#### In Project Mode, the Vivado IDE allows you to

- Define multiple implementation runs

Launch Runs...

Launch Step To

Reset Runs

€

- Run multiple strategies on a single design

- Customize implementation strategies to meet specific design requirements

- Save customized implementation strategies to use in other designs

- Non-Project Mode does not support predefined implementation runs and strategies

XII INX > ALL PROGRAMMABLE.

# **Run Implementation in Project Mode with Tcl**

launch\_runs [-jobs arg] [-scripts\_only] [-all\_placement] [-dir arg]

[-to\_step arg][-next\_step][-host args][-remote\_cmd arg]

[-email\_to args] [-email\_all] [-pre\_launch\_script arg]

[-post\_launch\_script arg] [-force] [-quiet] [-verbose] runs...

to\_step

- opt\_design, power\_opt\_design, place\_design, power\_opt\_design(post\_place)

- Phys\_opt\_design, route\_design, write\_bitstream

- -to\_step place\_design

- -to\_step "power\_opt\_design (Post-Place)"

launch\_runs impl\_1

launch\_runs impl\_2 -to\_step place\_design

cd {F:\Vivado\Tutorial\logic\_sim\XSim\_Tutorial.runs\impl\_2}

open\_checkpoint sinegen\_demo\_placed.dcp

launch\_runs impl\_2 -next\_step

#### **Run Implementation in Non-Project Mode**

```

1 # Step 1: Read in top-level EDIF netlist from synthesis tool

2 read edif c:/top.edf

3 read edif c:/core1.edf

4 read edif c:/core2.edf

5 # Step 2: Specify target device and link the netlists

6 link design -part xc7k325tfbg900-1 -top top

7 # Step 3: Read XDC constraints to specify timing requirements

8 read xdc c:/top timing.xdc

9 read xdc c:/top physical.xdc

10 # Step 4: Optimize the design with default settings

11 opt design

12 # Step 5: Place the design

13 place design

14 # Step 6: Route the design

15 route design

16 # Step 7: Run Timing Summary Report and Resource Utilization

17 report timing summary -file post route timing.rpt

18 report utilization -file post route utilization.rpt

19 # Step 8: Write checkpoint to capture the design database;

20 # The checkpoint can be used for design analysis

21 # in Vivado IDE or TCL API

22 write checkpoint post route.dcp

```

Non-project based designs must be manually moved through each step of the implementation process using Tcl commands

XILINX > ALL PROGRAMMABLE..

# place\_design

place\_design [-directive arg] [-no\_timing\_driven] [-unplace] [-cells args] [-post\_place\_opt] [-quiet] [-verbose]

#### -post\_place\_opt

- Potentially improve critical path timing at the expense of additional runtime

- This optimization can be run at any stage after placement, and can be particularly effective on a routed design

- The optimization examines the worst case timing paths and tries to improve placement to reduce delay

- The optimization is performed on a fully placed design with timing violations

- The -directive option controls the overall placement strategy, and is not compatible with any specific place\_design options.

```

place_design

phys_opt_design

route_design

place_design -post_place_opt

route_design

```

# route\_design

route\_design [-unroute] [-re\_entrant arg] [-nets args] [-physical\_nets] [-pin arg] [-directive arg] [-no\_timing\_driven] [-preserve] [-delay] [-free\_resource\_mode] -max\_delay arg -min\_delay arg [-quiet] [-verbose]

#### -preserve

Preserve existing routing

#### -delay

- Use with -nets or -pin option to route in delay driven mode

- -max\_delay

- Use with -pin option to specify the max\_delay constraint on the pin

-min\_delay

- Use with -pin option to specify the max\_delay constraint on the pin

```

route_design -delay -nets $myCriticalNets

route_design -preserve -directive RuntimeOptimized

route_design -unroute

```

# phys\_opt\_design

- > phys\_opt\_design [-fanout\_opt] [-placement\_opt] [-rewire] [-critical\_cell\_opt] [-dsp\_register\_opt] [-bram\_register\_opt] [-bram\_enable\_opt] [-shift\_register\_opt] [-hold\_fix] [-retime] [-force\_replication\_on\_nets args] [-directive arg] [-critical\_pin\_opt] [-quiet] [-verbose]

- Command options limit the optimization scope to only the specified options

- One option per optimization

# What Optimizations are Performed?

#### Timing-driven optimizations included by default

- Fanout: replicate drivers of high fanout nets

- Placement: move cells

- Rewiring: restructure logic cones

- Critical cells: replicate critical path cells

- DSP registers: move registers to/from DSP

- BRAM registers: move registers to/from BRAM

- Shift registers: move registers from SRLs

- Critical pins: swap physical LUT input pins

- Very high fanout: replicate drivers of very-high fanout nets

- BRAM enable: improve power-optimized BRAM enables

# What Optimizations are Performed?

#### > Optional optimizations

- Forced net replication: replicate regardless of timing slack

- Register retiming: balance registers across combinational delays

- Hold-fix: insert data path delay

#### **Summary**

- Different strategy may have different design flows with different directives

- Directive is incompatible with other options in opt\_design, place\_design, phys\_opt\_design and route\_design

- Directives and strategies provide alternate flows to try when the tool defaults don't meet timing on difficult designs

- Some Tcl command can help to meet timing

- place\_design –post\_place\_opt

- phys\_opt\_design

- route\_design –delay –nets

- Performance\_Explore is helpful for timing closure