这篇文章记录一下笔者剖析 NVDLA Compiler 工作机制的一些经过,在 NVDLA 的软件仓库中,Compiler与Runtime的源代码被放置在umd目录下,由同一个 Makefile 组织。

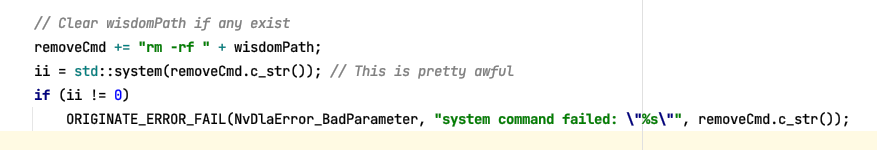

对于sw部分文档十分缺乏,在 NVDLA的页面里只有零星的介绍,而关于软件设计的细节、以及如何拓展设计都没有介绍。并且,Compiler这部分的代码充满了智慧,例如:

还有一些突然停止维护了而没开发完的feature。并且由于其前端只有 Caffe 的 Parser,导致其端到端的推理仅可以支持一些比较弱的分类网络,但阅读代码理解其设计与工作的思路,学习其抽象语法树的设计还是一个比较有意义的工作。