第一次讲直播课,主要分享的内容有:

- DL加速器/NPU概述

- NVDLA软件硬件栈简述与FPGA部署

- NVDLA存在的问题与Tengine后端适配方案介绍

Bilibili链接:https://www.bilibili.com/video/BV1z44y1478k

第一次讲直播课,主要分享的内容有:

Bilibili链接:https://www.bilibili.com/video/BV1z44y1478k

为接下来要尝试基于 Tengine 完成 CPU Fallback 的工作,在组里的 ZCU 102 开发板上进行了 NVDLA 的移植。本来以为这个过程会很顺利,没想到还是因为各种问题还是花费了一个星期的时间。

这篇文章记述了部分关于 ZCU102 rev1.1 板卡的坑点,以及利用chroot基于Ubuntu Base Rootfs来订制 aarch64 ubuntu 的文件系统流程。

这两天在京举办的第六届 ChinaDA 的学术研讨会是我第一次参加的学术会议,写下本文记述一下会议上比较感兴趣的点。篇幅不会长,主要是因为会前没有挑几个自己感兴趣的报告专门认真听一下,也没有没有做笔记、拍视频照片。

PS:这张大会的Banner页是我做的!

ChinaDA是国内集成电路设计、自动化没计(EDA)等学科青年学者自发组织的学术共同体,其使命是推动国内集成电路设计、EDA,及与之交叉的计算机体系结构和工艺器件等领城研究,为青年人搭建同行学术交流平台,提高本学科在国内科研界的地位。ChinaDA自2018年特殊时刻创建以来,每年举办2次,本次是第6届。

这篇文章记录一下笔者剖析 NVDLA Compiler 工作机制的一些经过,在 NVDLA 的软件仓库中,Compiler与Runtime的源代码被放置在umd目录下,由同一个 Makefile 组织。

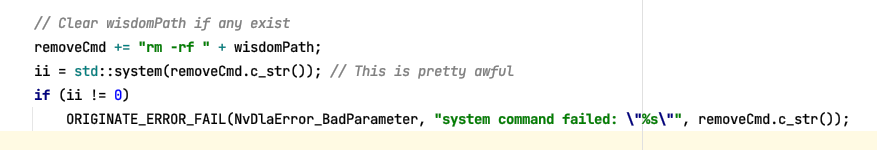

对于sw部分文档十分缺乏,在 NVDLA的页面里只有零星的介绍,而关于软件设计的细节、以及如何拓展设计都没有介绍。并且,Compiler这部分的代码充满了智慧,例如:

还有一些突然停止维护了而没开发完的feature。并且由于其前端只有 Caffe 的 Parser,导致其端到端的推理仅可以支持一些比较弱的分类网络,但阅读代码理解其设计与工作的思路,学习其抽象语法树的设计还是一个比较有意义的工作。

这篇是我在第一次参与的组会上分享的顶会论文,是我认识的一位博士发表的,其标题的含义大致是为具有鲁棒性的,由神经网络架构搜索出来的网络设计的加速器结构:

《NASGuard: A Novel Accelerator Architecture for Robust Neural Architecture Search (NAS) Networks》

Update your browser to view this website correctly. Update my browser now